其中,O/C表示模拟开关控制引脚(Open/Close)

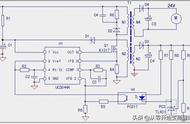

用P沟通JFET也可以组成模拟开关,但目前最常用的还是用MOSFET构成的开关,因为MOS技术是大规模数字集成电路的基础,这样可以在同一工艺下将模拟与数字功能实现在同一块芯片上,如下所示:

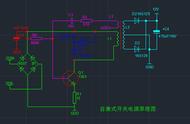

但是,无论是JFET或MOS构成的模拟开关,它们导通时漏-源通态电阻RDS(ON)都与栅-源电压VGS有关,而在输入信号Ui的变化过程中,VGS也是一直随之变化的,如下图所示:

在信号的传输过程中,真正施加在MOS管栅-源两极的电压VGS=-(15V-UO),而UO是与Ui相关的,如果输入信号Ui足够大的话,甚至会在信号传输过程中将MOS管关断,这显然不是我们想要的结果,因为我们的目标是得到一个恒定的(或比较恒定的)导通电阻RON。我们当然也希望导通电阻越小越好,但是在很多应用中,模拟开关的恒定通态电阻(导电率)是最重要的,也就是通态阻抗平坦度RDS(flat),因为它关乎输出电压的精度。

比如,用高精度ADC(模数转换器)进行多路电压信号采集时,模拟开关的导通电阻RON不必强制要求有多小,但只要它们的导通电阻RON是恒定的,可以在算法上将其带来的误差清除。

用一对互补MOSFET(即CMOS)即可消除这些缺点,它的结构如下图所示:

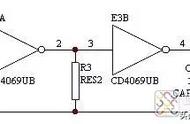

当O/C控制引脚为高电平时,Q1(PMOS)因栅-源电压VGS<VGS(ON)而导通(PMOS的导通阈值为负电压),同样,Q2(NMOS)因栅-源电压VGS>VGS(ON)而导通(NMOS的导通阈值为正电压),如下图所示: